You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

DIY BMS design and reflection

- Thread starter BiduleOhm

- Start date

Factory400

Solar Enthusiast

- Joined

- Jul 15, 2020

- Messages

- 387

They don't even have an e-stop input...

Yep, and actually it's easier to not trust it and not rely on it.

As I have mentioned on other threads - I am hardly concerned about MOSFETS or back-to-back MOSFETS as an ultimate backstop to a runaway problem.

I think I will have my new system setup with remote control signals connected as my first layer of shutdown control. Most likely it will work great for a very long time. Considering that only one single fault could tank the whole battery system - I will also have a bidirectional MOSFET switch as the final equivilant to the Halon System in data centers.

Dissipation is the primary concern, but that is easily solved in the number of MOSFETs in the design. The more MOSFETs, the less power is dissipated. At the same time, the more MOSFET's, the easier it becomes to manage the dissipation. MOSFET's are rather cheap.

With modern N-ch FETs in the sub-mOhm regions, this is not all that hard. Let's say a MOSFET has RdsON of 1mOhm. Back to back, 2mOhm.

16 FETs gets you 250uOhms or about 22 watts at 300 amps. That aint so bad and 1mOhm FETs are not all that expensive.

If you doubled the FET's again to 32 parts - You are down to 11 watts over 32 devices at a full 300A. Pretty amazing. At 340mW per device - dissipation is child's play.

Super vanilla devices in that range are about $1/ea so the 32FET solution only being $32 for the switching elements. Pretty good.

Of course their are fancier devices down into the 400uOhm range that are around $3/ea but you need a lot less of them to get the same dissipation. I would probably go that direction personally.

Factory400

Solar Enthusiast

- Joined

- Jul 15, 2020

- Messages

- 387

You'll not find MOSFETs with those specs at that price... Otherwise I would be using them ?

Just a quick pass.....

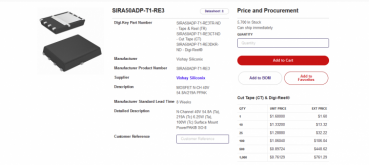

1.04mOhm https://www.digikey.com/en/products/detail/vishay-siliconix/SIRA50ADP-T1-RE3/9462341

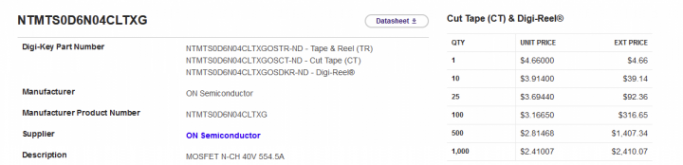

420uOhms https://www.digikey.com/en/products/detail/on-semiconductor/ntmts0d6n04cltxg/9829162

Factory400

Solar Enthusiast

- Joined

- Jul 15, 2020

- Messages

- 387

Of course - I just remembered your project is 48v.They are both 40 V max... You need at least 80 V ones.

More like $5/ea for 1.2mOhm

IPT012N08N5ATMA1 Infineon Technologies | Discrete Semiconductor Products | DigiKey

Order today, ships today. IPT012N08N5ATMA1 – N-Channel 80 V 300A (Tc) 375W (Tc) Surface Mount PG-HSOF-8-1 from Infineon Technologies. Pricing and Availability on millions of electronic components from Digi-Key Electronics.

What would you say your practical dissipation budget would be for a 300A switch? 16 of these would be about 36W - a little over 2W per device. Doesn't seem too terrible for $80.

The best compromise I found is those one: https://www.mouser.fr/ProductDetail...hyDBzk1/Wi/D7Em5shE8q79oNeZh9OawirCDuGpIRaw==

20 of them, and you can find all the dissipation values in the DPB table in this post

20 of them, and you can find all the dissipation values in the DPB table in this post

I’m out camping with limited reception. As I recall, the limiting factor for fet disconnects is the heat sink, not individual fets.For the total thermal power, yes, but the main limit is the individual thermal power and it'll be too high if you put only 1/4 of the MOSFETs because then you'll have double the current per MOSFETs so 4x the dissipated power per MOSFET.

He wants to do a separate port BMS with the discharge side MOSFETs switched and the charge side low current signal controlled.

I’m out camping with limited reception. As I recall, the limiting factor for fet disconnects is the heat sink, not individual fets.

You can redo the calculations if you want to be sure but I confirm that in my case the limiting factor is the individual thermal power, mainly because the PCB is in the thermal path. I have some margin of course but not that much, something like 30-50 % on top of using the worst case parameters, even if it's hard to have an exact number because there's not much data available (basically only one article) about using vias as a thermal path (almost all the articles are about using the PCB itself as the heatsink, not inbetween the components and an aluminium heatsink).

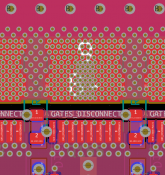

For the fun here's a capture for a single MOSFET:

Thermal vias are 0.32/0.6 mm, standard vias are 0.4/0.75 mm and the bigger vias are 0.8/1.4 mm.

Hedges

I See Electromagnetic Fields!

- Joined

- Mar 28, 2020

- Messages

- 20,535

I’m out camping with limited reception. As I recall, the limiting factor for fet disconnects is the heat sink, not individual fets.

That'll depend on thermal resistance theta J-C of the FET.

PCB as heatsink will provide some theta C-A (case to air) and you have to read the assumptions in the data sheet if relying on the figures they quote.

Discrete heatsink (with its own data sheet numbers depending on air flow) of course you can get a lot more.

I did a design using BJT, and big limitation for me was 12.5 degrees/watt theta J-C. That meant at 10 watts dissipation, 125 degree rise. Maximum junction temperature of 150C would be reached if case was held at 25 degrees C. Other transistors quoted much lower thermal resistance but I couldn't get the to work for me. I just had to minimize power dissipated in the transistor itself (power only does me any good in the load, but I was using it as a linear amplifier to drive a sine wave so best case a percentage of output power was the minimum dissipation it would have. Keep voltage rails close to maximum amplitude.

FETs for switching applications tend to have extremely low thermal resistance and Rds(on)

Hedges

I See Electromagnetic Fields!

- Joined

- Mar 28, 2020

- Messages

- 20,535

You can redo the calculations if you want to be sure but I confirm that in my case the limiting factor is the individual thermal power, mainly because the PCB is in the thermal path. I have some margin of course but not that much, something like 30-50 % on top of using the worst case parameters, even if it's hard to have an exact number because there's not much data available (basically only one article) about using vias as a thermal path (almost all the articles are about using the PCB itself as the heatsink, not inbetween the components and an aluminium heatsink).

For the fun here's a capture for a single MOSFET:

View attachment 36069

Thermal vias are 0.32/0.6 mm, standard vias are 0.4/0.75 mm and the bigger vias are 0.8/1.4 mm.

This is for a heatsink on the opposite side?

Looks like it would be way to many vias for good path in X and Y direction through copper plane. But good for reaching heatsink opposite side.

I just evaluate vias with Excel, based on barrel length and thickness.

Fan-out to sheet of copper before transfer to heatsink matters. It would seem like fanning out on surface layer is best, but one project some other guys did, solder mask adhesion to copper was poor and pulled away (heatsink epoxied to it.). Turned out to be better fanning out on a buried layer. May not be such a problem with bolts clamping heatsink.

I've seen vendor (and "engineer") recommendations for connecting to a sheet of copper on every layer between topside and bottom side. If an island isolated from ground plane, that doesn't do anything to help cooling; I use interleaved ground planes to carry heat away.

This is for a heatsink on the opposite side?

Yes

Looks like it would be way to many vias for good path in X and Y direction through copper plane. But good for reaching heatsink opposite side.

Yep, that's why there is far more of them than what's usually seen when the PCB is the heatsink.

I just evaluate vias with Excel, based on barrel length and thickness.

Interesting. I used those documents: https://www.ecomal.com/fileadmin/Da...rmal-Design-Guide-Enhancement-Mode-031815.pdf and https://www.ti.com/lit/an/snva419c/snva419c.pdf to estimate the number of vias I needed and found it was around 120. I was able to fit 160 of them (not counting those around the pad, nor the source side of the MOSFET which should help a bit too).

It'll be a 1.6 mm PCB with 70 µm copper and 25 µm via plating. Using this calculator I find 156 °C/W so that's conveniently almost exactly 1 °C/W total for 160 vias.

I want to have a Tj of 100 °C max at 1.7 W with 60 °C ambient.

The PCB temp increase is 1.7 °C.

The MOSFET Rthjc is 0.35 °C/W so that's a 0.6 °C increase.

Heatsink will be around 2 °C/W so 20 °C/W equivalent per MOSFET which is a 34 °C increase.

Thermal paste should be around 0.1 °C/W so 0.2 °C increase.

Solder should be even lower than the thermal paste but let's round to 0.1 °C/W too so 0.2 °C increase.

The total is then a 37°C increase for a 40 °C budget. As you can see there isn't that much margin so that's why I put as many vias as reasonable. And the good thing is that it matches pretty well with my initial number of vias estimation from the papers.

Fan-out to sheet of copper before transfer to heatsink matters. It would seem like fanning out on surface layer is best, but one project some other guys did, solder mask adhesion to copper was poor and pulled away (heatsink epoxied to it.). Turned out to be better fanning out on a buried layer. May not be such a problem with bolts clamping heatsink.

I planned 7x M3 bolts per heatsink so that shouldn't be a problem

I've seen vendor (and "engineer") recommendations for connecting to a sheet of copper on every layer between topside and bottom side. If an island isolated from ground plane, that doesn't do anything to help cooling; I use interleaved ground planes to carry heat away.

I don't have much PCB area around each MOSFET so this solution isn't really useful in my case.

Last edited:

Factory400

Solar Enthusiast

- Joined

- Jul 15, 2020

- Messages

- 387

This is the best part of the conversation so far - and the area where I have the most to learn.

Hedges

I See Electromagnetic Fields!

- Joined

- Mar 28, 2020

- Messages

- 20,535

Heatsink will be around 2 °C/W so 20 °C/W equivalent per MOSFET which is a 34 °C increase.

The total is then a 37°C increase for a 40 °C budget.

It's all hanging on the heatsink performance, then.

I've seen a range of specs for various brands, not all consistent with each other (performance vs. size.) Could be some quote air speed in a channel in which the heatsink is placed, and some present considerable resistance to airflow but quote velocity that is achieved between the fins.

One of my designs I ended up with a gap between heatsink of one board and the next board, seemed to me if I stuffed in some foam weather stripping it would divert airflow through the heatsink, boosting velocity. The heatsink was meant to be SMT straddling the transistor, and I used it that way for a single-sided prototype. For production version, transistors were on opposite side, one directly under each leg. I had plans for an additional heatspreader to land straddling the transistors and also carry heat to/through enclosure but that was never implemented.

I used a couple kinds for my BJT RF amp and for voltage regulators and MOSFETs on a second board. Selecting voltages for input power, regulated supply, voltage to load I was able to keep them all at suitable temperature rise. Power op-amps in SOIC had a body pad on a voltage rail, so those I spread out to about 1 cm^2 on an inner layer, sandwiched between ground planes. FR4 provided electrical insulation and enough thermal conduction so their ~ 1W or 2W could be spread over the board area and dissipated to air.

DA-T268-301E-TR Ohmite | Fans, Thermal Management | DigiKey

Order today, ships today. DA-T268-301E-TR – Heat Sink TO-268 (D³Pak) Aluminum 7.0W @ 35°C Top Mount from Ohmite. Pricing and Availability on millions of electronic components from Digi-Key Electronics.

219-263A-TR Wakefield-Vette | Fans, Thermal Management | DigiKey

Order today, ships today. 219-263A-TR – Heat Sink TO-263 (D²Pak) Aluminum 2.0W @ 30°C Top Mount from Wakefield-Vette. Pricing and Availability on millions of electronic components from Digi-Key Electronics.

Link for your heatsink?

Hedges

I See Electromagnetic Fields!

- Joined

- Mar 28, 2020

- Messages

- 20,535

Didn't find the thermal resistance easily for that; catalog link had that as a search parameter.

Large fin pitch of 12.5mm won't interfere much with air flow, should work decently for convection.

I haven't done anything in airflow analysis or thermal transfer, just "ohms law" with thermal parameters.

Forced air vs. passive will make a huge difference. My experience was something passively cooled (a vacuum pump) drawing a few watts was almost too hot to touch. With a tabletop fan aimed at it, it was stone cold. Our "Expert" said the pump's max ambient temperature spec limited the spec of our system to less than that figure. I attempted to explain (without success) that the part (a Pfeiffer pump) really didn't have a requirement for ambient temperature, rather case temperature. Once we determined case temperature in its specified 45C environment, by using a fan we could operate at higher environmental temperature such that derived case temperature spec was met.

Large fin pitch of 12.5mm won't interfere much with air flow, should work decently for convection.

I haven't done anything in airflow analysis or thermal transfer, just "ohms law" with thermal parameters.

Forced air vs. passive will make a huge difference. My experience was something passively cooled (a vacuum pump) drawing a few watts was almost too hot to touch. With a tabletop fan aimed at it, it was stone cold. Our "Expert" said the pump's max ambient temperature spec limited the spec of our system to less than that figure. I attempted to explain (without success) that the part (a Pfeiffer pump) really didn't have a requirement for ambient temperature, rather case temperature. Once we determined case temperature in its specified 45C environment, by using a fan we could operate at higher environmental temperature such that derived case temperature spec was met.

Yep, I had to estimate its rth by looking at other similar heatsinks.

Yes, it's common to see a factor of 3 to 5 between convection and even relatively low forced airflow. But I don't want to depend on a fan for this project.

Yes, it's common to see a factor of 3 to 5 between convection and even relatively low forced airflow. But I don't want to depend on a fan for this project.

Hedges

I See Electromagnetic Fields!

- Joined

- Mar 28, 2020

- Messages

- 20,535

Easy enough to measure if you can set up a representative air flow/restriction environment. Ought to do that if considering cutting down. However, projecting performance to a different length may be far from trivial.

As a BMS, it is going to disconnect battery for a variety of reasons.

Did you implement heatsink over-temperature as a reason for disconnect?

Do you expect convection to always keep it cool enough? If not, adding a thermostatic fan would extend it's capability,

As a BMS, it is going to disconnect battery for a variety of reasons.

Did you implement heatsink over-temperature as a reason for disconnect?

Do you expect convection to always keep it cool enough? If not, adding a thermostatic fan would extend it's capability,

Easy enough to measure if you can set up a representative air flow/restriction environment. Ought to do that if considering cutting down. However, projecting performance to a different length may be far from trivial.

I'll do real world tests for that

Did you implement heatsink over-temperature as a reason for disconnect?

Yes, there's two temp sensors (one per bank of MOSFETs) which will be thermally bonded to two of the MOSFETs.

Do you expect convection to always keep it cool enough? If not, adding a thermostatic fan would extend it's capability,

Yes.

There's a spare output on the BMS you will be able to trigger from a big list of events (including MOSFETs over temp of course) so you can add a fan easily if you want.

Correct.the 3000VA unit still only has one high-current connection that is both charge/discharge, right?

Are you talking about the remote control inputs?

I am using the temperature input of my 2000W Multiplus for the relay output of the BMV-712. The BMV-712 relay output is configured to stop charging on the basis of SOC% and cell temperature (low temperature charging disconnect). My understanding is that the 3000W Multiplus has an extra input that could be used to turn off the inverter as well. Not sure how I could use that, but I have been thinking about it from a theoretical standpoint.

Similar threads

- Replies

- 8

- Views

- 318

- Replies

- 11

- Views

- 555

- Replies

- 8

- Views

- 247

- Replies

- 15

- Views

- 493