Not sure what you mean. I have a small signal diode at the input to the linear regulator LM1117. The diode is for reverse voltage protection. I had already reverse voltage the circuit once, causing some of the chips to glow bright red! Yeah, I should be banned from touching any electronics.I don't think you should have those diodes on the input and output of your linear regulator. It should be ferrite beads on the input, if anything, and nothing in series with the output.

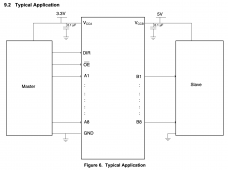

Also, use a real level-shifter and not one made manually out of fets.

One of the things considered is to use "real" level shifters. TI makes real low level shifters, not from 3.3V to 5V. There's some devices with open drains (SN74LVC1G07). They may work.

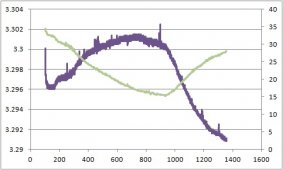

Regarding any errors caused by the resistor network to simulate cell voltages. The 390 ohm resistance is much smaller than the 100k input resistance to the opamp. I've also seen similar errors when connected to the real battery. The simulated cells are not the cause of the measurement error.

Edit, I now see you're talking about the diodes located in the JY-MCU module. That's not my design. The diodes are for protection. The module has a 3.3V output which I am not using. The diode connected to the 3.3V output is open circuit and a non-issue. I don't see the input diode to the linear regulator as an issue either.

Last edited: