Okey Guys,

apologies for being away all this while.

I'm in travel with limited connectivity, so please bear with me.

Lots of discussions going around, trying to sum them up w.r.t the design the way I understand them .

.

Few changes incorporated:

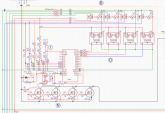

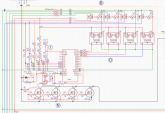

1) Transistor Opto(s) changed with Mosfet Opto(s).

2) R7 reduced to 4.7k.

3) Z1 Zener voltage Vz detected to verify PV state and activate charging functions (Through Digital Input).

4) Parallel Zeners(Z2) removed.

In Details:

Could this be due to excess current leak through pulldown resistor?

If that's the case can we substitute R7 with a smaller resistor(like 4.7k) to bring up the Zener current which could as well help maintain better zener regulation as suggested by @Cal .

Thanks for the calculations, they clear up things.

Now got a question for you: Iz would only exceed Iz(min) when Gates are active.

Since I'm now using Iz to verify PV state, can we connect a second pull down resistor from +ive end of capacitor C1 to enable sufficient Zener current leak to keep Zener regulation well above minimum levels?

apologies for being away all this while.

I'm in travel with limited connectivity, so please bear with me.

Lots of discussions going around, trying to sum them up w.r.t the design the way I understand them

Few changes incorporated:

1) Transistor Opto(s) changed with Mosfet Opto(s).

2) R7 reduced to 4.7k.

3) Z1 Zener voltage Vz detected to verify PV state and activate charging functions (Through Digital Input).

4) Parallel Zeners(Z2) removed.

In Details:

Thanks @Hedges , that's some nice simulation.I tried the regulator circuit in LTSpice with a couple substitutions using whatever was in the library.

Main problem I see is that 47k & 10k can't be at 12V unless Vpv > 68V

Using 47k pulldown seems to work. I does have a 5 ms time constant to turn off gate. Just so long as MOSFET has enough thermal mass to soak of the power dissipated in that time.

View attachment 20885

View attachment 20886

Could this be due to excess current leak through pulldown resistor?

If that's the case can we substitute R7 with a smaller resistor(like 4.7k) to bring up the Zener current which could as well help maintain better zener regulation as suggested by @Cal .

@Cal : Second zener removed on your insistence?.Vg = 35V * 10k/(47k + 10k) = 6.1V

The OP could be looking at a major disaster when on a cloudy day Vmp drops below 35V.

The correct way to design the zener circuit is for the bias resistor to account for the load current. Steady state load current is 12V/10k = 1.2 mA.

We'll include a buffer and say load current is 2 mA. Estimate min zener current at 5 mA. Not sure what the minimum Vmp can get down to? Estamate Vmp_min = 30V.

R7 = Vmp_min /( Iz_min + I_load)

R7 = 30V / (5 mA + 2 mA) = 4.2 k ohm

In addition, the second zener diode should be removed.

Thanks for the calculations, they clear up things.

Now got a question for you: Iz would only exceed Iz(min) when Gates are active.

Since I'm now using Iz to verify PV state, can we connect a second pull down resistor from +ive end of capacitor C1 to enable sufficient Zener current leak to keep Zener regulation well above minimum levels?