You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

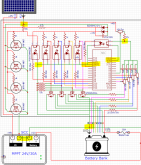

DIY All-In-One Solar Generator - Control Board

- Thread starter Bhupinder

- Start date

Hedges

I See Electromagnetic Fields!

- Joined

- Mar 28, 2020

- Messages

- 20,695

Is that an Arduino Nano in your schematic?

That has analog inputs too.

You can add a temperature sensor, for instance 10 k ohm NTC thermistor, biased with a pullup resistor and with an optional parallel resistor. Thermally bonded to the heatsink but electrically isolated, this lets you monitor its temperature. Another in the air could also let you monitor ambient temperature. If heatsink exceeds some maximum, turn off the MOSFETs because they're dissipating too much power. Wait until below some lower temperature (hysteresis) before turning back on. I like to do shutdown in hardware but that takes a circuit to do comparison & hysteresis, and you've got a microcontroller. Difference between heatsink and ambient is an indication of how much power.

If you like you can monitor PV voltage (which is only available from charge controller when MOSFETs are turned on.) Put two 100k resistors in series from 5V to GND, connect the midpoint to an analog input. Do that again to a second analog input. Differential voltage is zero, and input impedance of each resistor divider is 50k ohm. Put a 2M ohm resistor (or two, 1M in series) from one to PV positive, the other to PV negative. Each of those is a 41:1 divider, with 2.5V headroom to voltage rails. That will accept input in the range +/-102.5V while keeping Arduino inputs within zero to 5V, and 0.05 mA. Multiply the difference between those two inputs by 41 to get PV voltage.

Input voltages beyond the +5/GND rails are a no-no. If Arduino power is off, this circuit would deliver +2.5V beyond the rails given 50V PV, but limited to 0.025 mA which is probably OK because input protection diodes will clamp a small current. Microcontroller data sheet page 454 says +/- 0.5V relative to power/ground, limit current to 1 mA with a resistor.

Don't know about the Arduino boards, but the microcontrollers are rated either 85C or 125C. 85C is good for normal environments, with an enclosure and parts inside that might heat it up. If getting directly sunlight or mounted on/in same enclosure as power devices, best to have the 125C component.

That has analog inputs too.

You can add a temperature sensor, for instance 10 k ohm NTC thermistor, biased with a pullup resistor and with an optional parallel resistor. Thermally bonded to the heatsink but electrically isolated, this lets you monitor its temperature. Another in the air could also let you monitor ambient temperature. If heatsink exceeds some maximum, turn off the MOSFETs because they're dissipating too much power. Wait until below some lower temperature (hysteresis) before turning back on. I like to do shutdown in hardware but that takes a circuit to do comparison & hysteresis, and you've got a microcontroller. Difference between heatsink and ambient is an indication of how much power.

If you like you can monitor PV voltage (which is only available from charge controller when MOSFETs are turned on.) Put two 100k resistors in series from 5V to GND, connect the midpoint to an analog input. Do that again to a second analog input. Differential voltage is zero, and input impedance of each resistor divider is 50k ohm. Put a 2M ohm resistor (or two, 1M in series) from one to PV positive, the other to PV negative. Each of those is a 41:1 divider, with 2.5V headroom to voltage rails. That will accept input in the range +/-102.5V while keeping Arduino inputs within zero to 5V, and 0.05 mA. Multiply the difference between those two inputs by 41 to get PV voltage.

Input voltages beyond the +5/GND rails are a no-no. If Arduino power is off, this circuit would deliver +2.5V beyond the rails given 50V PV, but limited to 0.025 mA which is probably OK because input protection diodes will clamp a small current. Microcontroller data sheet page 454 says +/- 0.5V relative to power/ground, limit current to 1 mA with a resistor.

Don't know about the Arduino boards, but the microcontrollers are rated either 85C or 125C. 85C is good for normal environments, with an enclosure and parts inside that might heat it up. If getting directly sunlight or mounted on/in same enclosure as power devices, best to have the 125C component.

Yeah, got it. Source connects to PV ground, which has a lower potential than battery ground. Gate drive comes from PV power. This will work.They aren't at the same potential but they share the same ground which is PV negative.

Thanks @Hedges for all those suggestions. They are kind of on the list and more.

Got LM335s for temp and Hall effect sensor for current monitoring.

This board and automation control is a very late afterthought, had installed analog battery and power monitors already.

Still its fun to have the automation bit added for ease and safety I believe.

Originally Idea was to have 2 control boards - one at the battery end and other at the enclosure doing respective local duties.

Well now if I could convince myself to reduce Battery cable length shorter, then all could be had in a single board.

Sensors/ voltage monitoring and balancing leads running long lengths could result in inaccurate measurements and are prone to damage.

Thinking of adding a cell balance module next. Let me draw up a few things and shall get back for your valuable feedback!

Got LM335s for temp and Hall effect sensor for current monitoring.

This board and automation control is a very late afterthought, had installed analog battery and power monitors already.

Still its fun to have the automation bit added for ease and safety I believe.

Originally Idea was to have 2 control boards - one at the battery end and other at the enclosure doing respective local duties.

Well now if I could convince myself to reduce Battery cable length shorter, then all could be had in a single board.

Sensors/ voltage monitoring and balancing leads running long lengths could result in inaccurate measurements and are prone to damage.

Thinking of adding a cell balance module next. Let me draw up a few things and shall get back for your valuable feedback!

Hi,

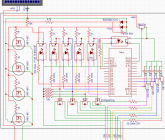

here's the draft schematic for 4S Cell balance module.

Idea is to monitor voltage of each individual cell ( via voltage divider) and short local electrodes once voltage reaches pre-determined top charge.

While exact algorithm for balancing can be done in microprocessor, dissipating excess charge is regulated via logic level Mosfet which is in series with electrodes of the cell. Since balance current is small ~150mA, I suppose logic level Mosfet should be able to do it without requiring explicit driver config.

Not sure how its done in commercial setups but using the same leads for Voltage monitoring and balancing could creep certain level of error in measurements. This could especially be true when Mosfet is active and Voltage at Positive junction of the voltage divider resistors drops slightly due to the burn load.

Please pour-in you comments/ suggestion if this makes any sense at all.

Regards

here's the draft schematic for 4S Cell balance module.

Idea is to monitor voltage of each individual cell ( via voltage divider) and short local electrodes once voltage reaches pre-determined top charge.

While exact algorithm for balancing can be done in microprocessor, dissipating excess charge is regulated via logic level Mosfet which is in series with electrodes of the cell. Since balance current is small ~150mA, I suppose logic level Mosfet should be able to do it without requiring explicit driver config.

Not sure how its done in commercial setups but using the same leads for Voltage monitoring and balancing could creep certain level of error in measurements. This could especially be true when Mosfet is active and Voltage at Positive junction of the voltage divider resistors drops slightly due to the burn load.

Please pour-in you comments/ suggestion if this makes any sense at all.

Regards

Attachments

Last edited:

That has analog inputs too.

You can add a temperature sensor, for instance 10 k ohm NTC thermistor, biased with a pullup resistor and with an optional parallel resistor. Thermally bonded to the heatsink but electrically isolated, this lets you monitor its temperature. Another in the air could also let you monitor ambient temperature. If heatsink exceeds some maximum, turn off the MOSFETs because they're dissipating too much power. Wait until below some lower temperature (hysteresis) before turning back on. I like to do shutdown in hardware but that takes a circuit to do comparison & hysteresis, and you've got a microcontroller. Difference between heatsink and ambient is an indication of how much power.

I prefer the TMP36 which is similar to the well known LM35 but has better specs. Its ouput is 10 mV/°C + 500 mV, so for example for 20 °C you have 700 mV, for 100 °C you have 1500 mV. Far easier to use than a NTC and more accurate without any calibration needed (but a bit more expensive)

If you like you can monitor PV voltage (which is only available from charge controller when MOSFETs are turned on.) Put two 100k resistors in series from 5V to GND, connect the midpoint to an analog input. Do that again to a second analog input. Differential voltage is zero, and input impedance of each resistor divider is 50k ohm. Put a 2M ohm resistor (or two, 1M in series) from one to PV positive, the other to PV negative. Each of those is a 41:1 divider, with 2.5V headroom to voltage rails. That will accept input in the range +/-102.5V while keeping Arduino inputs within zero to 5V, and 0.05 mA. Multiply the difference between those two inputs by 41 to get PV voltage.

That's super complex for nothing. Just use a simple voltage divider made with two resistors. If you want 100 k (PV side) and 10 k (GND side) will give you 11:1 attenuation so you can measure up to 55 V which should be plenty enough, add a second 10 k in parallel of the first one to get a 21:1 ratio and be able to measure up to 105 V if needed

I didn't check the input leakage current on the arduino nano but I bet it's pretty high so I'd avoid anything higher than 100 k (and even that might be a bit high still) to have reasonable accuracy.

Don't know about the Arduino boards, but the microcontrollers are rated either 85C or 125C. 85C is good for normal environments, with an enclosure and parts inside that might heat it up. If getting directly sunlight or mounted on/in same enclosure as power devices, best to have the 125C component.

If the arduino gets to 85 °C something isn't right with your design (unless you're on Mars or the moon maybe...), change whatever needs to be changed because all the components have a temp range and at 85 °C you'll have a lot of problems, not just with the MCU itself.

Hi,

here's the draft schematic for 4S Cell balance module.

View attachment 19972

Idea is to monitor voltage of each individual cell ( via voltage divider) and short local electrodes once voltage reaches pre-determined top charge.

While exact algorithm for balancing can be done in microprocessor, dissipating excess charge is regulated via logic level Mosfet which is in series with electrodes of the cell. Since balance current is small ~150mA, I suppose logic level Mosfet should be able to do it without requiring explicit driver config.

Not sure how its done in commercial setups but using the same leads for Voltage monitoring and balancing could creep certain level of error in measurements. This could especially be true when Mosfet is active and Voltage at Positive junction of the voltage divider resistors drops slightly due to the burn load.

Please pour-in you comments/ suggestion if this makes any sense at all.

Regards

Your balancing circuit will not work as only the mosfet nearest to GND will be able to be turned on by the MCU, the other ones have their source to a potential too high for the 5 V of the MCU to turn them on.

Also your divider network for the cell voltages is not wired correctly, and I'm pretty sure the resistor values are wrong.

Hedges

I See Electromagnetic Fields!

- Joined

- Mar 28, 2020

- Messages

- 20,695

That's super complex for nothing. Just use a simple voltage divider made with two resistors. If you want 100 k (PV side) and 10 k (GND side) will give you 11:1 attenuation so you can measure up to 55 V which should be plenty enough, add a second 10 k in parallel of the first one to get a 21:1 ratio and be able to measure up to 105 V if needed

He's got MOSFETs that isolated negative side of PV array from charge controller.

So how's your simple voltage divider made with two resistors going to let him measure PV voltage, again?

Buy 10 of each for $0.78 plus shipping, use 4 of each:

RC0805FR-07100KL YAGEO | Resistors | DigiKey

Order today, ships today. RC0805FR-07100KL – 100 kOhms ±1% 0.125W, 1/8W Chip Resistor 0805 (2012 Metric) Moisture Resistant Thick Film from YAGEO. Pricing and Availability on millions of electronic components from Digi-Key Electronics.

RC0805FR-0710KL YAGEO | Resistors | DigiKey

Order today, ships today. RC0805FR-0710KL – 10 kOhms ±1% 0.125W, 1/8W Chip Resistor 0805 (2012 Metric) Moisture Resistant Thick Film from YAGEO. Pricing and Availability on millions of electronic components from Digi-Key Electronics.

(I sometimes put two blocking elements in series for higher voltage)

Differential signals, nominally mid-range of the ADC, takes care of any voltage offset, whether PV negative goes to ground or is isolated.

A capacitor should be added from each ADC input to GND, filtering out noise of frequencies higher than your sample rate. Keep it low enough to study peak-search of controller, but attenuate switching noise if present.

Last edited:

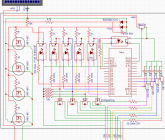

Update

Corrected Mosfet charging mechanism by using optocouplers as drivers which shall utilize charge from PV source for the purpose.

Since now multiple drivers are to fed - beefed up current from Zeeners as well.

For the Voltage divider network, now using 10k potentiometers (Input current ~1mA) since even with a nominal manufacturing tolerances of 5% accuracy could be an issue when detecting 0.001V. Also mapping things with a variable resistor could make-up for any miscalculations and % error in the process - what do you say? or is it better to use combination of fixed and variable resistors to keep feed consistent around 1mA?

For the capacitor part - should 1uF be fine or is it still too big to slow down voltage sensitivity? Unable to calculate capacitance, this one is just a wild guess.

As added protection from unwanted feed from voltage leads reaching microprocessor when its OFF (which could potentially destroy it)- have added an opto switch cutting off the common ground, which would allow feed voltages to reach ADC only when opto is activated on purpose. However now with the small capacitors @ ADC input - could they still not induce the same effect?

Please keep the criticism flowing, its addictive.

Regards!

Thanks @BiduleOhm for the critical review.Your balancing circuit will not work as only the mosfet nearest to GND will be able to be turned on by the MCU, the other ones have their source to a potential too high for the 5 V of the MCU to turn them on.

Also your divider network for the cell voltages is not wired correctly, and I'm pretty sure the resistor values are wrong.

Corrected Mosfet charging mechanism by using optocouplers as drivers which shall utilize charge from PV source for the purpose.

Since now multiple drivers are to fed - beefed up current from Zeeners as well.

For the Voltage divider network, now using 10k potentiometers (Input current ~1mA) since even with a nominal manufacturing tolerances of 5% accuracy could be an issue when detecting 0.001V. Also mapping things with a variable resistor could make-up for any miscalculations and % error in the process - what do you say? or is it better to use combination of fixed and variable resistors to keep feed consistent around 1mA?

Thanks @Hedges - Have picked direct feed from PV panels to monitor voltage across terminals and used 50k pot in similar fashion. Hoping that should work, cant't see why not.He's got MOSFETs that isolated negative side of PV array from charge controller.

So how's your simple voltage divider made with two resistors going to let him measure PV voltage, again?

(I sometimes put two blocking elements in series for higher voltage)

Differential signals, nominally mid-range of the ADC, takes care of any voltage offset, whether PV negative goes to ground or is isolated.

A capacitor should be added from each ADC input to GND, filtering out noise of frequencies higher than your sample rate. Keep it low enough to study peak-search of controller, but attenuate switching noise if present.

For the capacitor part - should 1uF be fine or is it still too big to slow down voltage sensitivity? Unable to calculate capacitance, this one is just a wild guess.

As added protection from unwanted feed from voltage leads reaching microprocessor when its OFF (which could potentially destroy it)- have added an opto switch cutting off the common ground, which would allow feed voltages to reach ADC only when opto is activated on purpose. However now with the small capacitors @ ADC input - could they still not induce the same effect?

Please keep the criticism flowing, its addictive.

Regards!

Attachments

Hedges

I See Electromagnetic Fields!

- Joined

- Mar 28, 2020

- Messages

- 20,695

1) PV positive gets divided by potentiometer before going to microcontroller, but not clear to me that PV negative also reaches microcontroller. (That is why described both connected, so you can read two ADC and compute the differential)

2) If you turn that pot too far one way, you get 45V straight into microcontroller. Should always have fixed resistors limiting that.

Whatever tolerance a resistor has, is also usually the variation in resistance it will show across its spec'd operating range. So a 5% resistor, even adjusted, may provide too much variation with temperature.

I usually use 0.1% resistors for any measurements. I suggested 1% for yours, figuring good enough and cheap.

Input voltages beyond power/ground rails are often most destructive when device is powered, causes "latchup".

Sufficiently high impedance so injected current stays within spec limits is usually good protection. There are some clamping devices, and with low input current those do their job.

2) If you turn that pot too far one way, you get 45V straight into microcontroller. Should always have fixed resistors limiting that.

Whatever tolerance a resistor has, is also usually the variation in resistance it will show across its spec'd operating range. So a 5% resistor, even adjusted, may provide too much variation with temperature.

I usually use 0.1% resistors for any measurements. I suggested 1% for yours, figuring good enough and cheap.

Input voltages beyond power/ground rails are often most destructive when device is powered, causes "latchup".

Sufficiently high impedance so injected current stays within spec limits is usually good protection. There are some clamping devices, and with low input current those do their job.

PV negative is not connected directly to microcontroller but it latchges to SCC ground when mosfets are activated. SCC is internally hardwired with Battery ground - which is common ground for the microcontroller also.1) PV positive gets divided by potentiometer before going to microcontroller, but not clear to me that PV negative also reaches microcontroller. (That is why described both connected, so you can read two ADC and compute the differential)

I am not sure if we can read less than '0' volts at microcontroller inputs (In case ground reference of PV is lower than that of microcontroller/battery since its floating) as it could easily damage the input pin.

I believe we would be able to gauge exact PV voltage only when its connects with battery ground through SCC.

Before that happen with open PV circuit condition, sensing anything in the range of 30-50V should be enough to confirm PVs are active and ready to latch. After all how far can the ground references go apart?

Do you think putting a 4.7v zener in parallel with resistance at each ADC input could help save from unwanted spikes/ accidental flashes?Input voltages beyond power/ground rails are often most destructive when device is powered, causes "latchup".

Sufficiently high impedance so injected current stays within spec limits is usually good protection. There are some clamping devices, and with low input current those do their job.

What other clamping components can be of use here?

I'm sorry but the schematic gets really hard to read as it gets more complex so if you can redraw it following the conventions it would be a lot easier for us (higher potentials to lower potentials from top to bottom and signals from left to right). Also please use components designators (R1, R2, Q1, Q2, ...) as it's a lot easier to refer to components while we discuss here.

You can't just up the voltage without taking into account where the grounds are and if they are common or not. Also you need to be careful about the Vgs as if you exceed the max the mosfet is dead.

And you can't increase the current to the zener indefinitely, you need to be careful about power dissipation (for example the poor 4.7 k resistor will dissipate 232 mW which is awfully close to the 250 mW standard rating so you'll need to jump to a 0.5 W resistor), and it's not needed here as there's the cap anyway and you only switch mosfets gates, you can keep the 47 k resistor you had before.

Do not use pots in precision voltage dividers, they are not accurate and they drift a lot with time and temp. You don't really care if the value of the resistors isn't exact as you'll calibrate the value in software anyway, it's more important to have low drift resistors (avoid carbon resistors, use metal film ones). If you really want more accurate resistors then get some, there's 1 % ones or even better at 0.5 % and 0.01 % for example, but price rise quickly and it's not worth it, just change the gain in software to match the DMM reading

Sounds more or less fine but hard to tell right now. Settle on the divider design first, the cap value will be chosen last

That's a super bad idea for lots of reason and uneeded as the MCU has clamping diodes. Just keep current low enough to not destroy said diodes (you'll find the max in the MCU datasheet) and/or add some TVS diodes to protect the inputs.

Yep, you (@Bhupinder ) need to have a differential input (you can use two inputs for that). What you do with PV+ you need to do it too for PV- and do the substraction PV+ - PV- in software to have a differential measurement. Or you can use a differential op-amp if you don't have an analog input to spare for that, but that's a another whole can of worms so let's avoid it for now...

No it can't, you can biais you divider to be able to measure negative voltages however. It would not damage the input if the resistors values are high enough.

As said just before: TVS. They're basically super zeners made exactly for that purpose.

Corrected Mosfet charging mechanism by using optocouplers as drivers which shall utilize charge from PV source for the purpose.

Since now multiple drivers are to fed - beefed up current from Zeeners as well.

You can't just up the voltage without taking into account where the grounds are and if they are common or not. Also you need to be careful about the Vgs as if you exceed the max the mosfet is dead.

And you can't increase the current to the zener indefinitely, you need to be careful about power dissipation (for example the poor 4.7 k resistor will dissipate 232 mW which is awfully close to the 250 mW standard rating so you'll need to jump to a 0.5 W resistor), and it's not needed here as there's the cap anyway and you only switch mosfets gates, you can keep the 47 k resistor you had before.

For the Voltage divider network, now using 10k potentiometers (Input current ~1mA) since even with a nominal manufacturing tolerances of 5% accuracy could be an issue when detecting 0.001V. Also mapping things with a variable resistor could make-up for any miscalculations and % error in the process - what do you say? or is it better to use combination of fixed and variable resistors to keep feed consistent around 1mA?

Do not use pots in precision voltage dividers, they are not accurate and they drift a lot with time and temp. You don't really care if the value of the resistors isn't exact as you'll calibrate the value in software anyway, it's more important to have low drift resistors (avoid carbon resistors, use metal film ones). If you really want more accurate resistors then get some, there's 1 % ones or even better at 0.5 % and 0.01 % for example, but price rise quickly and it's not worth it, just change the gain in software to match the DMM reading

For the capacitor part - should 1uF be fine or is it still too big to slow down voltage sensitivity? Unable to calculate capacitance, this one is just a wild guess.

Sounds more or less fine but hard to tell right now. Settle on the divider design first, the cap value will be chosen last

As added protection from unwanted feed from voltage leads reaching microprocessor when its OFF (which could potentially destroy it)- have added an opto switch cutting off the common ground, which would allow feed voltages to reach ADC only when opto is activated on purpose. However now with the small capacitors @ ADC input - could they still not induce the same effect?

That's a super bad idea for lots of reason and uneeded as the MCU has clamping diodes. Just keep current low enough to not destroy said diodes (you'll find the max in the MCU datasheet) and/or add some TVS diodes to protect the inputs.

1) PV positive gets divided by potentiometer before going to microcontroller, but not clear to me that PV negative also reaches microcontroller. (That is why described both connected, so you can read two ADC and compute the differential)

Yep, you (@Bhupinder ) need to have a differential input (you can use two inputs for that). What you do with PV+ you need to do it too for PV- and do the substraction PV+ - PV- in software to have a differential measurement. Or you can use a differential op-amp if you don't have an analog input to spare for that, but that's a another whole can of worms so let's avoid it for now...

I am not sure if we can reads less than '0' voltages at microcontroller inputs (In case ground reference of PV is lower than that of microcontroller/battery since its floating) which would easily damage the input pin.

No it can't, you can biais you divider to be able to measure negative voltages however. It would not damage the input if the resistors values are high enough.

Do you think putting a 4.7v zener in parallel with resistance at each ADC input could help save from unwanted spikes/ accidental flashes?

What other clamping components can be of use here?

As said just before: TVS. They're basically super zeners made exactly for that purpose.

Looks like cells can only be balanced while solar is operational.

There is a price to pay when using a low side disconnect switch. You’re now dealing with several grounds. This gets messy.

Though I’ve been away from designing quite a while, I think a high side disconnect switch is a better way to go. No reason to shy away from P-channel fets.

Now there’s just one common ground.

There is a price to pay when using a low side disconnect switch. You’re now dealing with several grounds. This gets messy.

Though I’ve been away from designing quite a while, I think a high side disconnect switch is a better way to go. No reason to shy away from P-channel fets.

Now there’s just one common ground.

Yes Cal, its intentional to activate balancing only during charge cycle.Looks like cells can only be balanced while solar is operational.

We can let it be there across all phases and hence the small balance current.

True, trying to rearrange things so we just have to deal with one ground for internal circuitry while the other ground comes into picture only during PV charging process.There is a price to pay when using a low side disconnect switch. You’re now dealing with several grounds. This gets messy.

Yes, logically its always better to go with a clearer design but we have following concerns here:Though I’ve been away from designing quite a while, I think a high side disconnect switch is a better way to go. No reason to shy away from P-channel fets.

Now there’s just one common ground.

1) Have already ordered most of the components which are in shipping as we speak (Long shipping times already).

2) More importantly, can't find good enough P-channel FETs that could cover Vds voltage of 45-50v with safe margins

and delivery enough current without exceeding power loss limits.

From whats available - would have to put at least 10 mosfets in parallel if not more to get 30Amp continuous.

Here is the list for your ref: https://www.electronicscomp.com/index.php?route=product/search&search=p-channel mosfet

@BiduleOhm & @Hedges What do you guys suggest? Is it prudent to abort PV negative isolation plan and go with P-channel mosfets at this stage or we remain on course?

What do you guys suggest? Is it prudent to abort PV negative isolation plan and go with P-channel mosfets at this stage or we remain on course?

If you know what you're doing negative switching is fine and just require some isolation here and there, usually optos. It avoids the P-MOS inconvenients and the high-side drive circuitry needed.

The grounds are connected only when solar is active. That means it’s impossible to balance cells when the grounds are not connected. Will you have a secondary charging source? You won’t be able to balance then.

You can still use your N-Channel fets for a high side switch. That’s what BiduleOhm uses in his design.

You can still use your N-Channel fets for a high side switch. That’s what BiduleOhm uses in his design.

Hedges

I See Electromagnetic Fields!

- Joined

- Mar 28, 2020

- Messages

- 20,695

I've used or seen both high-side and low side in a project that had too many cooks.

Issues that arose were high-side NMOS switches needing to either be fast (PWM to control fan speed) or continuous (remain on/off) with the wrong choice between charge-pump and capacitor boot circuits, also low-side where an RS-485 signal went between boards causing over voltage/current to burn out a driver.

By sticking with NMOS low-side or PMOS high-side the drive circuit is simple.

Communicating between circuit domains with opto-isolators, relays, resistors for differential signalling, or digital isolators, solves voltage reference issues.

Resistors are so cheap (on an SMT PCB, where layout and assembly is basically coding, unlike manual breadboards) that I use them a lot. My "super complex" resistor circuits are balanced so they perform stably over temperature and voltage. In most cases I use 0.1% thin-film resistors to maintain 0.1% or better performance over temperature. Even when measuring a single-ended signal with a differential input ADC or op-amp I put an identical resistor network on the other input. When measuring an attenuated high voltage, self-heating of the resistor can drive it toward the 0.1% spec so I use a larger size to reduce heating, trying improve matching by factor of ten. When I needed ppm level measurements I discovered Vishay metal-film resistors. They add $10 to $50 to a design (!) but are what's used in DMM with 1 ppm accuracy.

I figure for your cell balancing you'd like 0.1% measurements, but for PV voltage and current 2% is fine.

You have to consider all cases of power present/absent and switches on/off, make sure none of them would overstress a part.

Issues that arose were high-side NMOS switches needing to either be fast (PWM to control fan speed) or continuous (remain on/off) with the wrong choice between charge-pump and capacitor boot circuits, also low-side where an RS-485 signal went between boards causing over voltage/current to burn out a driver.

By sticking with NMOS low-side or PMOS high-side the drive circuit is simple.

Communicating between circuit domains with opto-isolators, relays, resistors for differential signalling, or digital isolators, solves voltage reference issues.

Resistors are so cheap (on an SMT PCB, where layout and assembly is basically coding, unlike manual breadboards) that I use them a lot. My "super complex" resistor circuits are balanced so they perform stably over temperature and voltage. In most cases I use 0.1% thin-film resistors to maintain 0.1% or better performance over temperature. Even when measuring a single-ended signal with a differential input ADC or op-amp I put an identical resistor network on the other input. When measuring an attenuated high voltage, self-heating of the resistor can drive it toward the 0.1% spec so I use a larger size to reduce heating, trying improve matching by factor of ten. When I needed ppm level measurements I discovered Vishay metal-film resistors. They add $10 to $50 to a design (!) but are what's used in DMM with 1 ppm accuracy.

I figure for your cell balancing you'd like 0.1% measurements, but for PV voltage and current 2% is fine.

You have to consider all cases of power present/absent and switches on/off, make sure none of them would overstress a part.

You can still use your N-Channel fets for a high side switch. That’s what BiduleOhm uses in his design.

Technically I still switch the low side because I have other things on the same board that aren't isolated and needs to be referenced to the battery negative, but apart from that, yes, the main disconnect is totally isolated and could switch the positive side no problem. But the drive circuitry is a lot more complex than a small mosfet and a few resistors, as I'm using an isolated DC/DC converter and isolated gate driver ICs; we try to avoid all that here.

Resistors are so cheap (on an SMT PCB, where layout and assembly is basically coding, unlike manual breadboards) that I use them a lot. My "super complex" resistor circuits are balanced so they perform stably over temperature and voltage. In most cases I use 0.1% thin-film resistors to maintain 0.1% or better performance over temperature.

Yea of course. But my point was that it was more complex than necessary, especially as we don't need 0.1 % for PV voltage as you said and as he wants to stay TH which is understandable. Also when I wrote that I was thinking he didn't need a differential measurement, so of course that would have made things a lot simpler ?

Also my main concern would be the 2 M resistors, that's pretty high and I'm pretty sure the MCU input leakage current will skew the measurements far more than any resistor tempco mismatch, etc. Also we're talking about an on-board ADC with only 12 bits and an internal Vref (which is notoriously crappy...) so more like 10 ENOB at best; so 0.1 % will be a single LSB at that point, you would need oversampling to get back to a more accurate measurement.

Hedges

I See Electromagnetic Fields!

- Joined

- Mar 28, 2020

- Messages

- 20,695

Also my main concern would be the 2 M resistors, that's pretty high and I'm pretty sure the MCU input leakage current will skew the measurements far more than any resistor tempco mismatch, etc. Also we're talking about an on-board ADC with only 12 bits and an internal Vref (which is notoriously crappy...) so more like 10 ENOB at best; so 0.1 % will be a single LSB at that point, you would need oversampling to get back to a more accurate measurement.

The impedance I propose to him was actually 2M || 100k || 100k = 48.78k (thevenin equivalent impedance) which should be fine for driving a high-impedance analog input. At least in terms of DC. Some unbuffered ADC inputs charge a sampling cap, so capacitor across the input supplies that in addition to being part of an RC filter.

Good point on oversampling. There's a lot more bits available so long as you have enough random noise. Maybe don't decouple inputs as well as I suggested? I've put capacitors on ADC inputs, and I've oversampled data into a scope, but I haven't played with input capacitance vs. recovering more bits resolution than is native to the ADC.

I'm just now getting into characterizing a circuit with sigma-delta ADC. That's a one-bit ADC that outputs a pwm (or similar) bit stream and has feedback. Then some digital filtering that I don't know anything about. Similar idea as oversampling, except it measures error of last conversion, rather than taking High/Low measurement of signal plus noise (although that could be part of the scheme too.) Years ago I worked with a 1 bit ADC (comparitor) built into a chip as an analog sampling head per pin or other circuit of interest. That used an external DAC to hunt and find levels.

Similar threads

- Replies

- 0

- Views

- 139

- Replies

- 37

- Views

- 995

- Replies

- 39

- Views

- 2K