NB: Currently I put this project on pause, it's definitely not abandonned but I'm very busy on other projects, mainly working on my house (it was pretty much only walls and a roof when I bought it so there's lots of work). Once I have those done I'll continue on the BMS, design is almost done and then comes prototyping and testing which will be a big part of the project.

Hello. I've come over this thread recently and I'd like to join the conversation. I started with my BMS about year ago, with different design and probably a different goal but I hope we can share some experiences. I'll try to respond to several interesting points in this thread below.

Different but also similar with the added busbar on the PCB for example

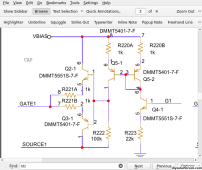

MOSFET opening by high dV/dt has already bitten me. Most new drivers use "miller clamp" so that you don't need to worry but in my BMS I drive 32 mosfets on different voltage levels so that I needed simple/cheap solution:

But for existing clamp-less driver it is simple to add one PNP to do it. See e.g.

ROHM-clamp-AN.

Very interesting to know it is a problem IRL because so far everyone told me it's likely not a problem and that the engineers who wrote the 2 or 3 papers I based my calculations on were splitting hairs.

As you probably saw I solved the problem (at least in theory) by adding a capacitor between the gate and source and a diode (so I can still turn off the FETs as quickly as possible) which I think is the most compact and cost effective way of doing it, especially since a BJT based miller clamp also needs a cap. It's also a design confirmed to work IRL in half and H bridges for the top FET who see the source voltage change quickly when the bottom FET switches, altho they typically use far smaller caps, in the nF range for a few reasons. It's basically rising the Cgs artificially so the Cgd/Cgs capacitive divider has a higher ratio so Vgs can't go above the Vgsth with whatever Vds your design is using.

IIRC the gate driver I used have a clamp but I'm not sure it works when the driver is unpowered. I prefer to have an additional way to solve the problem right at the FET pins (just the track inductance from the driver to the gate can be a problem here given the PCB is quite big) and I planned to run tests anyway to see what happens IRL.

32 FETs? that's a lot, is it for current capability or for advanced features?

For TVS clamping of wires. Twin cabling has approx 1uH/1m, I have 8m of 2x25mm2 wires and I measured 12uH. I crafted simple tester (see pic below) where I use 15uH/200Asat inductor and big (10mohm ESR) cap plus big 500A (IIRC) mosfet.

You can see 56V 1.5kW SMB transil - it blowed up at 80A pulse. Then I used THT 5KP51A and it survives 140A and the voltage over it was clamped to 72V. The 1.5K SMB transil was able to clamp only to 110V when still alive. Thus I use 80V MOSFETs too (SiR582).

Yep, I added a few big TVS to help the FETs but I still think they will go into avalanche on very inductive loads. Even if I don't like it a lot it should be fine as they are avalanche rated and I don't have another practical solution beside going with higher Vds FETs so only the TVS are conducting on a spike (but it means they would be more expensive and I would need more of them because of the higher Rdson...).

This branch is connected to external 2R2/20W resistor and is used to precharge invertor caps on first connect and to balance newly connected battery if it is more than 0.4V from others.

Interesting. I have a very similar design and I wonder how you determined the 0.4 V threshold? I didn't settled on the threshold I will use yet but was thinking to use the minimal realistic resistance between two packs wired together and the maximum current I want flowing between them to calculate it.

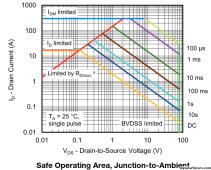

In the last comment I've wanted to introduce myself. I'd like to ask for opinions about mosfet SOA and speed of turn-on/off. There was very nice overview by (IIRC) BiduleOhm. For SiR582 we have SOA:

I'm interested if one can extrapolate for shorter pulses than 100us. Basicaly I strive for e-fuse like in BiduleOhm design, just now I use 1k gate resistor fo have about 1us on/off time. I slowed it down from original 100ns because there was too much ringing on the verge of avalanche.

As you can see it's exponential from 10 s to 1 ms but then it doesn't follow the same trend anymore for the 100 µs curve so it'll be very hard to extrapolate. You best bet is asking the manufacturer. But at the 1 µs time scale you probably can assume the Idm will be your limit anyways and that's a hard limit mainly depending on the bond wires, silicon, etc. and not the thermal limit.

1 k sounds very high for a gate resistor (for example I have 20 Ohm for turn-on and 15 for turn-off), those FETs must have a very low gate charge I guess.

It seems to me that battery turn-on time is dictated by smallest possible wiring inductance on ONE side of switch (I assume single point of failure design so that I expect one side of switch can be shorted but not both).

For 1uH (1m) minimum we have for 60V rise 60A/us. If you can switch under 1us you are in the SOA (at 100us power limit line). But if I could extrapolate extra 10us line then I can switch-on over time of 10us which would help ringing...

Yes, exactly. If you can't switch super slowly (like 1 ms) then you're probably running a bit too close to the limit of the FET and I would advise to see if it's ok to get a beefier one. It should make your life a lot easier, for other things too like your SOA problem (but it would cost a bit more of course)

Regarding turn-off event. ACS711 has 1.3us FAULT delay to overcurrent 31A, it goes to MCU interrupt line, MCU latency is 400ns. So that

over these 2us the current already rise to 150A. Hence I guess turn-off should be as fast as possible. And we need to solve ringing/inductive kick by other means (snubbers, TVS).

Am I correct ?

Yes, you're 100 % correct. I basically arrived at the conclusion you can't do e-fuse with the MCU, it's too slow (well in theory you can if you use a crazy fast MCU which would be more a SoC than a MCU at that point...). Doing it in HW is also quite simple (basically just a comparator), you just need to keep the speed in mind for everything in the chain (fast comparator, no low-pass filter, low capacitive loading, good decoupling, ...) but that's pretty much it. I also hate having a something as critical as a e-fuse run in SW (and I'm a SW architect and developper ?).

NB: you can forget the snubber solution (I explored that path too) as it would need LOTs of capacitance (think mF to F, not nF or µF...), it's not practical. Maybe a small-ish one just to help another type of clamp is possible tho.